## 令 和 二 年 度 修 士 論 文

ゲート端子の接続探索および GAとDPを複合した素子値決定による設計精度の向上

指導教員 髙井 伸和 准教授

群馬大学大学院理工学府 理工学専攻 電子情報・数理教育プログラム

今野 哲史

# 目次

| 目次                             | 1  |

|--------------------------------|----|

| 第1章 研究背景・目的                    | 3  |

| 1.1 研究背景                       | 3  |

| 1.2 研究目的                       | 3  |

| 1.3 本論文の構成                     | 5  |

| 1.4 設計の流れ                      | 5  |

| 1.4.1 ゲート端子の接続探索の流れ            | 5  |

| 1.4.2 GA と DP を複合した素子値の自動決定の流れ | 7  |

| 第2章 GA と DP の理論                | 9  |

| 2.1 GA の概要                     | 9  |

| 2.2 DP と強化学習                   | 10 |

| 第3章 GA によるゲート端子の接続先探索          | 11 |

| 3.1 ゲート端子の接続探索へ GA の適用         | 11 |

| 3.2 探索手順                       | 11 |

| 3.2.1 初期値の作成                   | 12 |

| 3.2.2 環境適応度                    | 16 |

| 3.2.3 GA による遺伝子操作              | 17 |

| 3.3 シミュレーション方法及び回路特性の評価方法      | 19 |

| 3.3.1 電源電圧 (SV)                | 20 |

| 3.3.2 消費電流(CC)                 | 20 |

| 3.3.3 消費電力(PD)                 | 20 |

| 3.3.4 出力抵抗(OR)                 | 21 |

| 3.3.5 直流利得(DC Gain)            | 21 |

|                                | 22 |

| 3.3.6 位相余裕 (PM)                | 23 |

| 3.3.7 利得帯域幅積(GBP)              | 23 |

| 3.3.8 入力換算雑音(IRN)              | 24 |

| 3.3.9 スルーレート (SR)              | 24 |

| 3.3.10 全高調波歪(THD)              | 26 |

| 3.3.11 同相除去比(CMRR)               | 26 |

|----------------------------------|----|

| 3.3.12 電源電圧変動除去比(PSRR)           | 27 |

| 3.3.13 同相入力範囲(CMIR)              | 29 |

| 3.3.14 出力電圧範囲(OVR)               | 30 |

| 3.3.15 最低要件                      | 32 |

| 第4章 遺伝的アルゴリズムと動的計画法を複合した素子値の自動設計 | 33 |

| 4.1 遺伝的アルゴリズム(GA)と動的計画法(DP)      | 33 |

| 4.1.1 GA と DP の特徴                | 33 |

| 4.1.2 素子値の自動設計への応用               | 36 |

| 4.2 素子値の自動決定手順                   | 38 |

| 4.2.1 初期値の作成                     | 38 |

| 4.2.2 環境適応度                      | 38 |

| 4.2.3 個体からエージェントへの進化             | 39 |

| 4.3.4 GA による遺伝子操作                | 39 |

| 4.3.5 DP による探索                   | 40 |

| 第 5 章 <b>実行結果</b>                | 42 |

| 5.1 ゲート端子の接続先探索の結果               | 42 |

| 5.2 GA と DP を複合した素子値設計の結果        | 45 |

| 第6章 まとめと今後の課題                    | 48 |

| 6.1 まとめ                          | 48 |

| 6.2 今後の課題                        | 48 |

| 謝辞                               | 48 |

| 参考文献                             | 49 |

## 第1章 研究背景・目的

### 1.1 研究背景

「アナログ・デジタル混載集積回路」が多く製造されている近年、AIの発達や小型デバイスの開発が著しく、LSIの更なる高性能化が求められている。現在、デジタル回路設計は、論理合成技術を用いた論理設計工程の自動化が成され短期間での開発が可能である。一方で、要求仕様に応じて適切なトポロジーの選択だけでなく、回路特性の複雑なトレードオフを考慮して設計しなければならないアナログ回路設計は、設計の難易度が高く自動合成の手法が確立していない。そのため、設計者の知識や経験に基づき、試行錯誤を繰り返しながら要求仕様を満たす回路を設計している。つまり、LSIの開発期間の大部分をアナログ回路の設計時間が占めている。また、設計者の技量や主観に依存度が大きいアナログ回路の設計時間が占めている。また、設計者の技量や主観に依存の大きいアナログ回路設計では、設計者を継続的に育成する必要もあり、コストがかかったり設計者不足を招いたりしている。そこで、コンピュータで実現可能な、技術者の知識やスキルに依存しないアナログ回路の自動合成手法を実現し、問題の解決を図る。

## 1.2 研究目的

アナログ回路の自動合成では、回路構成を決定するステップと素子値を決定するステップに分けられている。回路構成を決定するステップで構成を変化させ、異なる回路構成が生まれる度に、何度も素子値を割り振って性能を評価して素子値を決定している。それを繰り返すことで学習を行う。回路構成を決定するプロセスにランダム性が高いほど不十分な学習となり、目標を満足する回路構成を発見することが困難になる。また、回路構成を決定した後に素子値を決定するため、回路特性を直接引き出すのは素子値決定の精度に依存する。そこで、本研究ではアナログ回路の中でも演算増幅器を対象とし、自動合成の精度向上を目指して回路構成の一部の自動合成と素子値の自動設計を行う。具体的に述べると、回路を自動合成するための要素として、素子の種類や配置、端子の接続など様々なものが考慮されている。合成手法としてはそれらの要素を、設計者の知識に基づき回路を機能別にブロック化して最適な組み合わせを学習させるブロックレ

ベルの手法 $^{(1)\sim(2)}$ や、素子単位で配置や接続を学習させる素子レベルの手法 $^{(3)\sim(4)}$ などが 提案されている。 前者の場合では設計者の知識や経験に基づき、素子の配置や端子を接 続して電流経路を確保したり回路的な機能を持たせたりした機能別ブロックを登録す る。そして、アルゴリズムを用いて機能別ブロックの適切な組み合わせを学習すること で回路を合成している。後者の場合では、ランダムもしくは一定の法則に従い素子を並 べた後、電流経路を確保するように素子の端子を接続する。そしてアルゴリズムを用い て素子の配置や電流経路について学習を行う。どちらの場合でも学習されるのは素子の 種類、配置、電流経路が主であり、MOSFET のゲート端子はランダムに接続されるこ とが多い。しかし、同等の素子の種類や配置、電流経路でもゲート端子の接続先によっ て回路の性能は大きく異なるため、未探索のままでは回路性能は不明である。同等の回 路構成でもう一つ回路性能を大きく左右するものが素子値である。素子値の自動設計で は、強化学習による演算増幅器の素子値の自動設計(5)~(9)や深層学習による演算増幅器 の素子値の自動決定<sup>(9)~(10)</sup>等が提案されている。本研究では回路構成の自動設計の一環 として、素子値の自動設計を行うことが前提のため、未知の回路にも対応できる強化学 習を応用した自動設計について検討した。強化学習による学習では結果が初期値に依存 することや、局所解に陥ってしまうという課題がある。

本研究ではアナログ回路の自動合成の設計精度を向上させるため、ゲート端子の接続先を探索する手法と、素子値の自動設計を行う手法を提案する。これにより、未発見の回路構成の早期発見や回路特性の向上を目指す。ゲート端子の接続探索では探索の手法として遺伝的アルゴリズム(GA: Genetic Algorithm)を用いる。任意のゲート端子を除いた素子配置・接続を持つ回路構成を入力として与えることで、目標値を満足するのに適したゲート端子の接続先を探索する。回路内のゲート端子がどこの端子に接続しているか行列を用いて管理する。これに GA の遺伝子操作を適応することで、ランダムで決定するよりも適切なゲート端子の接続先を決定した。また、素子値の自動決定では探索の手法として、GA と動的計画法(DP: Dynamic Programing)を組み合わせて用いる。二つの手法では探索範囲や探索経路が異なるために、組み合わせることで互いの短所を補い合い、長所を生かすことができる。それにより、単一のアルゴリズムよりも設計精度の向上を確認した。

## 1.3 本論文の構成

本論文は第6章で構成される。まず、第2章で本論文に用いているアルゴリズムの概要について述べる。次に、第3章でGAを応用したゲート端子の接続先を自動合成する手法について報告する。続いて、第4章でGAとDPを組み合わせた素子値の自動設計方法について報告する。そして、第5章で本研究において合成および設計された回路の性能を確認し、設計精度が向上できたかを確認する。最後に、第6章で本論文のまとめと今後の課題を述べる。

### 1.4 設計の流れ

#### 1.4.1 ゲート端子の接続探索の流れ

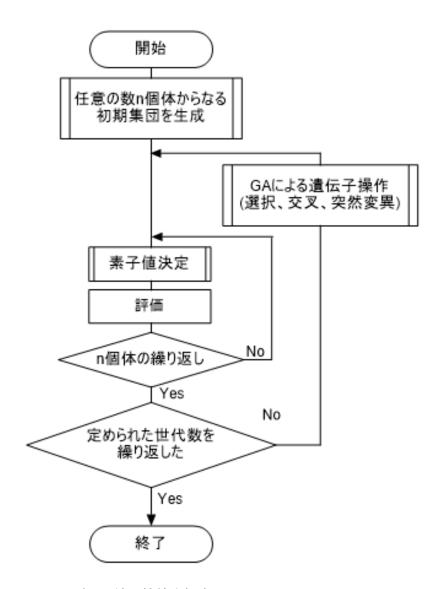

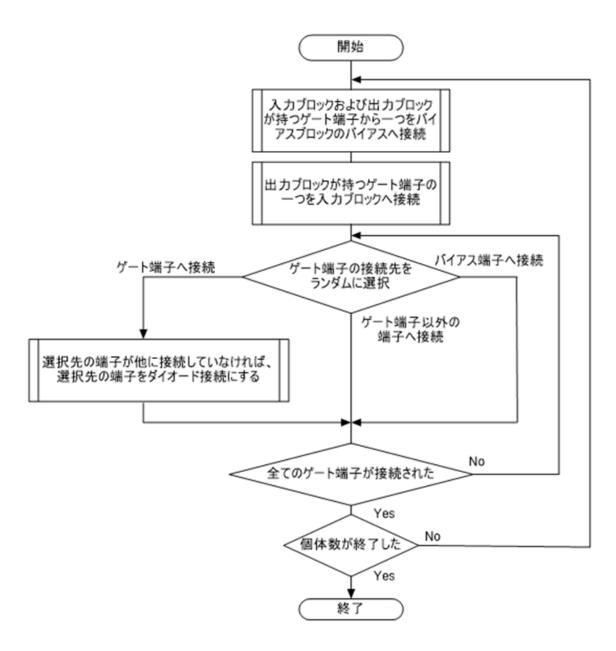

図1.1に本章におけるゲート端子の接続先を探索する流れを示す。提案手法では入力として任意のゲート端子のみが未接続状態の回路構成を与え、プログラムの最初に任意の個数の初期個体を作成する。各個体は特性が目標値を目指して素子値の探索を行い、最優秀な特性を用いて評価を行う。素子値の自動設計については第4章で詳しく説明する。その後、GAにより選択、交叉、突然変異の操作を施すことでゲート端子の接続先を変更し、次世代の個体群を作成する。そして再び各個体に対して素子値の決定と評価を行う。プログラムは GAによる操作から評価までを、任意の回数繰り返すことで終了する最終的に最も評価値の高かった個体1つを結果として出力する。

図1.1 ゲート端子接続先探索のフローチャート

#### 1.4.2 GA と DP を複合した素子値の自動決定の流れ

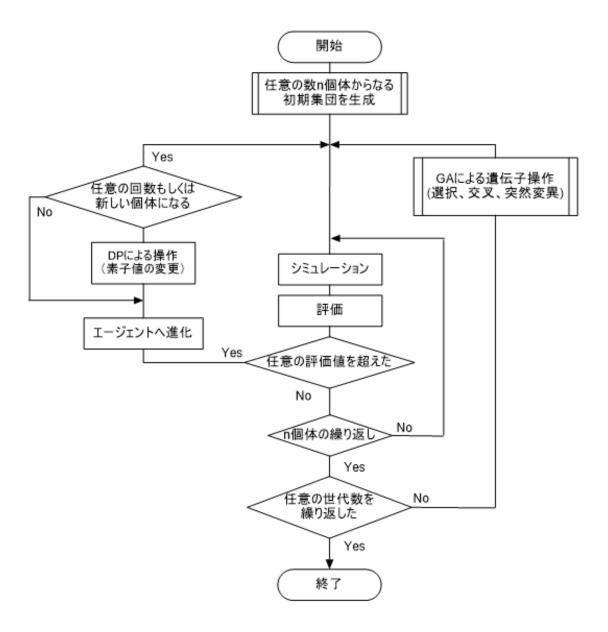

図1.2に本手法における素子値の自動設計の流れを示す。プログラムはまず与えられた回路構成から素子値のみを持つ初期集団を作成する。初期集団は任意の数の個体から形成される。各個体に対しシミュレーションを行い、結果を基に評価を与える。評価値が任意に定めた閾値を超えた個体は学習の主体をエージェントに変え、DPにより学習を行う。エージェントは世代が変わるときに自身が持つ素子値を僅かに変化させる。変化の度合いと結果から評価を行い学習させる。エージェントが素子値を変化させるとき、その評価を基準にする。エージェント以外の個体は GAにより選択、交叉、突然変異の操作が施され、次世代の個体群を作成する。プログラムは GAによる操作およびDPによる学習から評価までを、任意の回数繰り返すことで終了する。最終的に最も評価値の高かった個体1つを結果として出力する。

図1.2 素子値の自動設計のフローチャート

## 第2章 GAとDPの理論

### 2.1 GA の概要

GAとは生物の進化の過程を模倣し、近似解を求めるアルゴリズムである。GAでは最適化対象が持つパラメータを"遺伝子"、遺伝子の集まりを"染色体"と呼称する。最適化対象は染色体によって特徴を持ち、自律的な"個体"となる。最適化の手法として、最初に複数の個体からなる個体群を用意する。個体は環境(目標)に合わせて評価が行われる。個体群に対し、評価結果を基準にして"選択(淘汰)"した後、"交叉"により遺伝子の交換や"突然変異"によって遺伝子を変化させる。「選択」は評価を基に遺伝子操作の対象を選ぶ動作である。「交叉」「突然変異」はともに遺伝子操作を行う動作であるが、

「交叉」は大きく染色体を変化させるのに対し、「突然変異」は小さく染色体を変化させる。これらの遺伝子操作の後、変化した個体に対して再び評価を行う。この選択から評価までの一連の操作を得た個体群を次世代へ引き継ぎ、世代を重ねることで個体群は染色体中のスキーマを評価が高くなるように学習していき、近似解へと辿り着くことができる。

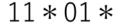

ここで言うスキーマとは遺伝子の集団に保持される部分集合を差し、0、1、\*(don't care)からなる文字列である。図 2.1 にスキーマの一例とそれを含む文字列を示す。

110010、110011、111010、111011

図2.1 スキーマの一例とそれを含む文字列

### 2.2 DP と強化学習

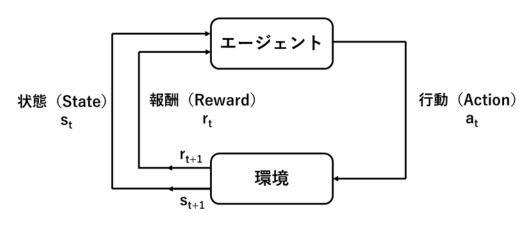

DP はマルコフ決定過程を解くための標準的なアプローチであり、最適化対象を複数の部分問題に分割し、部分問題の計算結果を記憶しながら解を導く手法の総称である。また、DP では一度計算した結果を記憶し再利用するため、同じ計算は繰り返さない。DP において問題が大規模になっても解けるように実践的なアルゴリズムに落とし込んだものが強化学習とも言え、強化学習は DP によって価値関数を更新していく手法である。代表的なものでは価値反復法や、方策反復法などがある。説明の分かりやすさから、ここでは強化学習について述べておく。強化学習では学習の主体となるものを「エージェント」と呼び、制御対象を「環境」と呼ぶ。エージェントは報酬の最大化を目指し、時点 t での環境の状態 s(t)に応じて行動 a(t)を行う。エージェントの行動により環境は状態 s(t+1)へ遷移し、それに応じた報酬 r(t)を与える。その後、行動に対する価値関数を更新し、時点 t を t+1 に進める。この一連の動作を繰り返す。図 2.2 に強化学習のフレームワークを示す。

図2.2 強化学習のフレームワーク

## 第3章 GAによるゲート端子の接続先探索

## 3.1 ゲート端子の接続探索へ GA の適用

GAによって最適化を行う場合、最適化対象が持つ特徴を"遺伝子"によって表現しなければならない。本章では与えられた回路構成に対し、未接続の MOSFET のゲート端子の接続先を決定するのが目的である。従って、回路構成の中で"ゲート端子がどの端子に接続されているか"という情報を遺伝子とする。この情報をプログラムでは行列で管理し、行列に対して GAによる遺伝子操作を行うことで行列に変化を与える。この行列は回路構成を示すものであるから、結果として GA の遺伝子操作によって回路構成が変化し、探索が行える。

## 3.2 探索手順

本節ではゲート端子の接続先の探索手順について、順番に説明していく。本章は自動合成の過程で機能別ブロックとして電流経路を基準に、バイアスブロック、入力ブロック、出力ブロックが作成されると仮定している。また、探索対象はブロック同士を接続するためのゲート端子の接続先やブロック内で未接続のゲート端子の接続先である。

ゲート端子が接続可能な端子は、他の MOSFET のゲート端子、素子が2つ以上接続されている回路内の端子もしくは、電源のいずれかである。このとき、ゲート同士だけが接続して他の端子のどこにも接続されないと、ゲート端子の電位は定まらない。それを防ぐために、ゲート端子同士が接続される場合、ゲート端子以外のどこかの端子とも必ず接続する。これは GA によって遺伝子操作が施され、接続が変わったとしても維持されていなければならない。そのため、本章ではゲート端子同士が接続する場合、「接続している」側と、「接続されている」側の両者を明確にして管理する。詳細は3.2.3 項の(b)目で述べる。

#### 3.2.1 初期値の作成

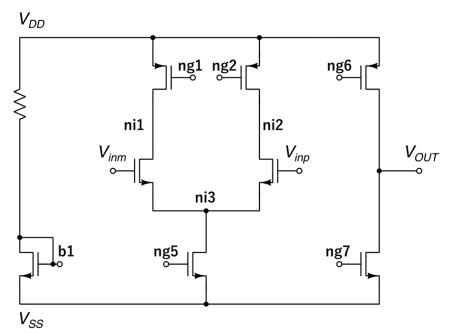

初期集団は図3.1に示すフローチャートに従って作成する。初期集団となる個体を作成するには、プログラムに探索したい回路構成を与える。具体的には、接続先を決定したいゲート端子名、ゲート端子がある素子のソース端子名、ゲート端子以外の端子名、電源名、ネットリストが必要となる。ネットリストは SPICE 形式に従い、各端子名と対応させる。探索したい回路の一例として図3.2、その回路図と対応する回路構成の端子名とネットリストを図3.3に示す。プログラムは開始時にこれらを基にして、図3.4に示すような行列を作成する。この行列は、列には「ゲート端子+ゲート端子以外の端子」を持つ。次に、ゲート端子の接続先を決定する。このとき、以下の六つのルールに従う。

- ・ゲート端子は一つずつ順番に接続先を選択する。

- ・ゲート端子を接続するとき、行列のゲート端子と接続先端子が交わる成分にフラグを 立てる。

- ・ゲート端子同士が接続する場合、行列では対角成分より右側にフラグを立てる。

- ・ゲート端子の接続先として他のゲート端子が選択された場合、フラグを選択している側の端子名(プログラム内では要素数)とする。また、選択された側の端子はダイオード接続となるようにフラグを立てる。

- ・ゲート端子以外と接続するときはフラグを1としている。

- ・ゲート端子ごとに一つのみ接続先を選択する(選択される場合は含まない)。

また、初期個体の作成段階で機能別ブロックが余らないように制限をかけてゲート端子を接続させる。まず、出力ブロックが持つゲート端子の一つを入力ブロックの持つ端子へと接続する。次に、入力ブロックと出力ブロックの持つゲート端子の中から1つをバイアスブロックのバイアス端子へと接続する。最後に、それ以外のゲート端子を他の端子へと無作為に接続する。この行列を任意の数生成し、初期集団とする。作成された行列の一例を図3.5、その行列が示す回路図を図3.6に示す。

図3.1 初期集団作成の流れ

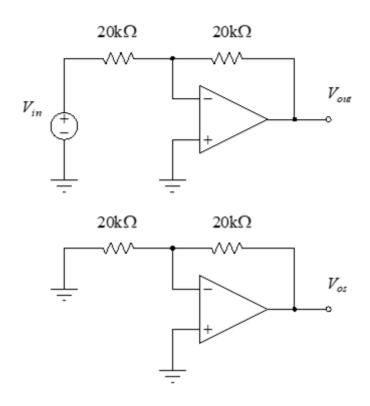

図3.2 探索したい回路図の一例

NetList

RB1 vdd nb1 resistance1

MB1 nb1 nb1 vss vss cmosn length1 width1

Ml1 ni1 ng1 vdd vdd cmosp length2 width2

Ml2 ni2 ng2 vdd vdd cmosp length3 width3

Ml3 ni1 inm ni3 vss cmosn length4 width4

Ml4 ni2 inp ni3 vss cmosn length5 width5

Ml5 ni3 ng5 vss vss cmosn length6 width6

MO2 out ng6 vss vss cmosn length7 width7

MO1 out ng7 vdd vdd cmosp length8 width8

SearchNode\_D ng1,ng2,ng5

SearchNode\_O ng6,ng7

BiasNoden b1

DiodNode\_D ni1,ni2,ni3

NomalNode\_D ni1,ni2,ni3

DiodNode\_O out,out

NomalNode\_O out

Voltage vdd, vss

図3.3 プログラムに与える端子名とネットリスト

|    |     |     | 探索  | するゲート | 端子  |     |     | ゲート端子 | 以外の端子 |     | バイアス<br>端子 | 電   | 源   |

|----|-----|-----|-----|-------|-----|-----|-----|-------|-------|-----|------------|-----|-----|

|    |     | ng1 | ng2 | ng5   | ng6 | ng7 | ni1 | ni2   | ni3   | out | b1         | vdd | VSS |

| 探索 | ng1 |     |     |       |     |     |     |       |       |     |            |     |     |

| する | ng2 |     |     |       |     |     |     |       |       |     |            |     |     |

|    | ng5 |     |     |       |     |     |     |       |       |     |            |     |     |

| +  | ng6 |     |     |       |     |     | ·   |       |       |     |            |     |     |

| 端子 | ng7 |     |     |       |     |     | ·   |       |       |     |            |     |     |

図3.4 端子名とネットリストを基に作成した行列

|        |     |     | 探索  | するゲート | 端子  |     |     | ゲート端子 | 以外の端子 | <u> </u> | バイアス<br>端子 | 電   | 電源  |  |

|--------|-----|-----|-----|-------|-----|-----|-----|-------|-------|----------|------------|-----|-----|--|

|        |     | ng1 | ng2 | ng5   | ng6 | ng7 | ni1 | ni2   | ni3   | out      | b1         | vdd | vss |  |

| 探索     | ng1 |     | ng2 |       |     |     | 1   |       |       |          |            |     |     |  |

| する     | ng2 |     |     |       |     |     |     |       |       |          |            |     |     |  |

| ゲ      | ng5 |     |     |       |     |     |     |       |       |          | 1          |     |     |  |

| <br> - | ng6 |     |     |       |     |     |     | 1     |       |          |            |     |     |  |

| 端子     | ng7 |     |     |       |     |     |     |       |       |          | 1          |     |     |  |

図 3.5 ゲート端子の接続先決定後の行列の一例

図 3.6 図 3.5 が示す回路図

#### 3.2.2 環境適応度

各回路構成(個体)は個体集団の中で優劣を定める必要がある。優劣は環境適応度(適応度)と呼ばれる値によって決定され、どれだけ環境(目標値)に沿っているかを表す。本研究で扱う回路特性については3.3節で示す。適応度は二段階の評価によって算出される。一段階目は各特性が最低要件を満たした割合で算出し、各項目につき1が最大値となる。最低要件を満たす条件は各項目で異なるため、その条件と評価方法を表3.1に示す。適応度は全ての特性の評価を加算したものとなる。全ての項目において最低要件を満たした場合のみ二段階目の評価値が適応度に加算される。二段階目は各特性が目標値を満たした場合で算出される。このとき、目標値を超えた項目の評価が大きくなり過ぎると適応度の中で他の項目の支配率が下がってしまい、目標値を目指しづらくなるためlogによってある程度の制限をかける。目標値を持たす条件によって評価が異なるため、その条件と評価方法を表3.2に示す。

表 3.1 最低要件を満たす条件と評価方法

| 最低要件を満足する条件 | 評価                |

|-------------|-------------------|

| 最低要項以下      | <u>結果</u><br>最低要件 |

| 最低要項以上      | 最低要件<br>結果        |

| 項目外         | 0                 |

表 3.2 目標値を満足する条件と評価方法

| 目標値を満足する条件 | 目標値を満たす前の評価   | 目標値を満たした後の評価                                                        |

|------------|---------------|---------------------------------------------------------------------|

| 目標値以下      | 目標値<br>       | $1 + log_{1000} \left( \frac{\exists 標値}{\exists \ddagger} \right)$ |

| 目標値以上      | 結果<br><br>目標値 | $1 + log_{1000} \left( \frac{$ 結果}{目標値} \right)                     |

| 項目外        | 0             | 0                                                                   |

#### 3.2.3 GA による遺伝子操作

本項ではGAにより回路構成を変化させるための、「選択(淘汰)」「交叉」「突然変異」 について説明する。

#### (a) 選択(淘汰)

個体集団を次世代に引き継いだときに、集団内での優秀な個体が劣化しないようにするために、「エリート個体保存戦略」を用いる。「エリート個体保存戦略」では個体集団内で適応度順に優秀な個体の一定割合をエリートとして、遺伝子操作をせずにそのまま次世代へと引き継ぐ。それとともに個体集団からエリート以外で次世代に引き継ぐ個体を作為的に選ぶ。選択方式によって収束の具合等が異なるため、本章では「トーナメント選択」を用いる。この選択方式では交代集団から無作為に一定数の個体を取り出し、その中から一番適応度の高い個体を次世代へ残す。この動作を次世代に必要な個数になるまで繰り返す。

#### (b) 交叉

交叉の手法にはいくつかの種類があるが、本章では多点交叉を用いる。この交叉方法は既存の二つの個体において、それぞれ染色体を複数に分割し、同じ位置にあるものをいくつか交換して新たな染色体を作成する。本章では行列が染色体であるため、行列上で、同一の位置にある成分を交換することで交叉とする。行列上でフラグが立っている場合、接続先を変化させたいゲート端子からみて「接続している」フラグが立っている成分のみ交叉が適応される。それにより、各ゲート端子は一つだけ「接続している」フラグを持つことになり、ゲート端子が浮くことはない。このとき、ゲート端子からみて「接続されている」フラグはいくつあってもよい。回路構成を示す行列に「交叉」適用する様子を図 3.7 に示す。図 3.7 では(a)と(b)の個体を交叉し、(c)と(d)の個体が作成される様子である。

|        |     |     | 探索  | するゲート | 端子  |     |     | ゲート端子 | 以外の端子 |     | バイアス<br>端子 | 電   | 源   |

|--------|-----|-----|-----|-------|-----|-----|-----|-------|-------|-----|------------|-----|-----|

|        |     | ng1 | ng2 | ng5   | ng6 | ng7 | ni1 | ni2   | ni3   | out | b1         | vdd | vss |

| 探索     | ng1 |     |     |       |     |     |     |       |       |     | 1          |     |     |

| する     | ng2 |     |     |       |     |     |     |       |       |     | 1          |     |     |

| ゲ      | ng5 |     |     |       |     | ng5 |     |       |       |     |            |     |     |

| <br> - | ng6 |     |     |       |     |     | 1   |       |       |     |            |     |     |

| 端子     | ng7 |     |     |       |     |     |     |       |       | 1   |            | ·   | ·   |

### (a) 交叉前の個体 1

|        |     | ,   | 探索  | するゲート | 端子  |     | ゲート端子以外の端子 |     |     |     | バイアス<br>端子 | 電   | 源   |

|--------|-----|-----|-----|-------|-----|-----|------------|-----|-----|-----|------------|-----|-----|

|        |     | ng1 | ng2 | ng5   | ng6 | ng7 | ni1        | ni2 | ni3 | out | b1         | vdd | vss |

| 探索     | ng1 |     |     |       |     |     |            |     |     | 1   |            |     |     |

| する     | ng2 |     |     | ng2   |     |     |            |     |     |     |            |     |     |

| ゲ      | ng5 |     |     |       |     |     |            |     | 1   |     |            |     |     |

| ۱<br>۱ | ng6 |     |     |       |     |     |            | 1   |     |     |            |     |     |

| 端子     | ng7 |     |     |       |     |     |            |     |     |     | 1          | ·   |     |

#### (b) 交叉前の個体 2

|    |     |     | 探索  | するゲート | 端子  |     | ゲート端子以外の端子 |     |     |     | バイアス 電 端子 |     | 源   |

|----|-----|-----|-----|-------|-----|-----|------------|-----|-----|-----|-----------|-----|-----|

|    |     | ng1 | ng2 | ng5   | ng6 | ng7 | ni1        | ni2 | ni3 | out | b1        | vdd | vss |

| 探索 | ng1 |     |     |       |     |     |            |     |     |     | 1         |     |     |

| する | ng2 |     |     | ng2   |     |     |            |     |     |     |           |     |     |

|    | ng5 |     |     |       |     | ng5 |            |     |     |     |           |     |     |

| ١  | ng6 |     |     |       |     |     | 1          |     |     |     |           |     |     |

| 端子 | ng7 |     |     |       |     |     |            |     |     |     | 1         |     |     |

## (c) 交差後の個体 1

|     |     |     | 探索  | するゲート | 端子  |     |     | ゲート端子 | 以外の端子 | :   | バイアス<br>端子 | 電   | 源   |

|-----|-----|-----|-----|-------|-----|-----|-----|-------|-------|-----|------------|-----|-----|

|     |     | ng1 | ng2 | ng5   | ng6 | ng7 | ni1 | ni2   | ni3   | out | b1         | vdd | vss |

| 探索  | ng1 |     |     |       |     |     |     |       |       | 1   |            |     |     |

| する  | ng2 |     |     |       |     |     |     |       |       |     | 1          |     |     |

| 1   | ng5 |     |     |       |     |     |     |       | 1     |     |            |     |     |

| 1 ' | ng6 |     |     |       |     |     |     | 1     |       |     |            |     |     |

| 端子  | ng7 |     |     |       |     |     |     |       |       | 1   |            |     |     |

## (d) 交差後の個体 2

図 3.7 交叉の様子

18

#### (c) 突然変異

突然変異ではゲート端子一つの接続先を変更する。行列上で、「接続している」フラグをフラグが立っていない他の成分へと移動させる。突然変異の前の個体を図 3.8 の(a) に、突然変異後を(b)に示す。

|        |     |     | 探索  | するゲート | 端子  |     | ゲート端子以外の端子 |     |     |     | バイアス<br>端子 | 電   | 源   |

|--------|-----|-----|-----|-------|-----|-----|------------|-----|-----|-----|------------|-----|-----|

|        |     | ng1 | ng2 | ng5   | ng6 | ng7 | ni1        | ni2 | ni3 | out | b1         | vdd | vss |

| 探索     | ng1 |     | ng2 |       |     |     | 1          |     |     |     |            |     |     |

| する     | ng2 |     |     |       |     |     |            |     |     |     |            |     |     |

| ゲ      | ng5 |     |     |       | ng6 |     |            |     |     |     | 1          |     |     |

| ۱<br>۱ | ng6 |     |     |       |     |     |            |     |     |     |            |     |     |

| 端子     | ng7 |     |     |       |     |     |            |     |     |     | 1          |     |     |

(a) 突然変異前の個体

|          |     |     | 探索  | するゲート | 端子  |     |     | ゲート端子 | 以外の端子 |     | バイアス<br>端子 | 電   | 源   |

|----------|-----|-----|-----|-------|-----|-----|-----|-------|-------|-----|------------|-----|-----|

|          |     | ng1 | ng2 | ng5   | ng6 | ng7 | ni1 | ni2   | ni3   | out | b1         | vdd | vss |

| 探索       | ng1 |     | ng2 |       |     |     | 1   |       |       |     |            |     |     |

| する       | ng2 |     |     |       |     |     |     |       |       |     |            |     |     |

| ゲ        | ng5 |     |     |       |     |     |     |       |       |     | 1          |     |     |

| <b> </b> | ng6 |     |     |       |     |     |     | 1     |       |     |            |     |     |

| 端子       | ng7 |     |     |       |     |     |     |       |       |     | 1          |     |     |

(b) 突然変異後の個体

図 3.8 突然変異の様子

## 3.3 シミュレーション方法及び回路特性の評価方法

本節では本研究における回路のシミュレーション方法及び回路特性の評価方法を説明する。シミュレーションには回路解析ツールである HSPICE を用いた。また、回路特性の評価項目、シミュレーション方法及び評価関数については 2020 年演算増幅器設計コンテスト(11)を参考にした。以下に特性ごとのシミュレーション方法を説明する。

#### 3.3.1 電源電圧 (SV)

電源電圧は 3V 以下とし、本研究では両電源を±1.5V とした。

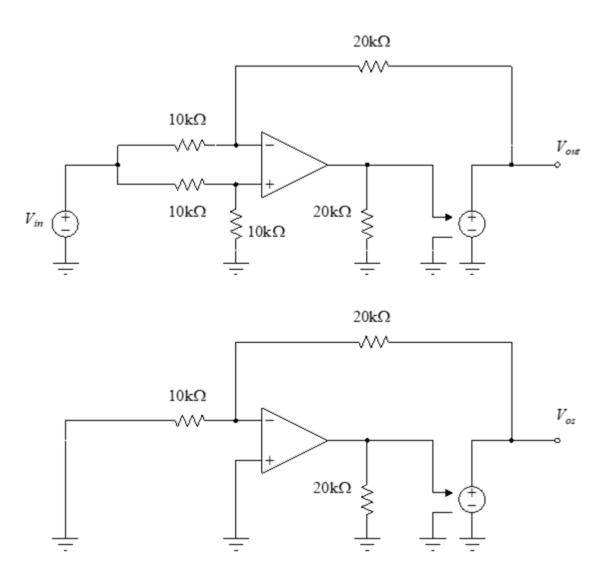

### 3.3.2 消費電流 (CC)

消費電流は図 3.9 に示す回路を用いて解析する。測定する値は無信号時において演算増幅器に流れる電流の大きさである。無信号時とは図 3.9 の回路において非反転入力端子が設置されるときのことである。このとき、演算増幅器がオフセット電圧を持つと、負荷となっている帰還抵抗に直流電流が流れ、 $V_{DD}$ から流れ出る電流または  $V_{SS}$  に流れ込む電流のどちらかがより大きくなる。そのため、バイアス電流は両方の電圧のうち大きい側の電流を回路の消費電流とする。

また、PVT の変動に対する回路性能を評価するため、電源電圧と温度を変化させてシミュレーションを行う。表 3.3 に示すように、電源電圧を設定した値かつ温度を 25度で解析した際のバイアス電流の大きさを  $I_0$ とし、電源電圧を設定した値の $\pm 10\%$ 、温度を $\pm 40\%$ C、 $\pm 25\%$ C及び  $\pm 80\%$ Cと設定した際のバイアス電流の大きさを  $\pm 1.8\%$   $\pm 1.8\%$

## 3.3.3 消費電力 (PD)

消費電力には、設定した電源電圧と算出した消費電流の値を使用する。電源電圧と消費電流の積を消費電力と定義する。

図 3.9 CC, OR, IRN, SR, THD の算出に用いる回路

表 3.3 バイアス電流の安定性評価

|          |         | 温度 [°C] |             |             |

|----------|---------|---------|-------------|-------------|

|          |         | -40     | 25          | 80          |

| 電源電圧 [V] | 設定値×0.9 | $I_{I}$ | $I_2$       | $I_{\beta}$ |

|          | 設定値     | $I_{4}$ | $I_{\it O}$ | $I_{5}$     |

|          | 設定値×1.1 | $I_{6}$ | $I_7$       | $I_{8}$     |

#### 3.3.4 出力抵抗(OR)

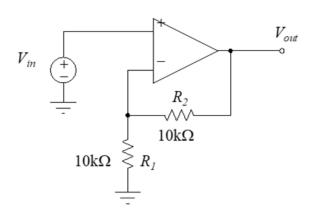

出力抵抗は図 3.8 に示す回路を用いて伝達関数解析する。伝達関数は  $V_{IN}$ から  $V_{OUT}$ までの小信号伝達を求めるものである。ここで小信号伝達は直流におけるものであり、利得、出力抵抗、入力抵抗の値が出力される。

演算増幅器は大きな直流利得を持つため、バイアス点を適切に定めるために負帰還をかけて解析を行う。図 3.8 についても抵抗 R 1 及び R 2 によって負帰還が構成されている。この状態で伝達関数解析を行うと、負帰還がかかる閉ループの出力抵抗値が出力される。そのため、実際の出力抵抗値を得るには、解析結果を補正する必要がある。演算増幅器の実際の出力抵抗を  $r_0$ とすると、出力抵抗の解析値  $r_{0-sim}$  との関係は次式で表される。

$$r_0 = \frac{1 + \beta A_{0-sim}}{\frac{1}{r_{o-sim}} - \frac{1}{R_1 + R_2} - \frac{\beta A_{0-sim}}{R_L}}$$

(3.1)

ここで  $A_{0\text{-}sim}$  は直流利得の解析による算出結果(次項参照)、 $R_L$  は直流利得を求める際の負荷抵抗であり 20k $\Omega$ 、 $R_I$ = $R_2$ =10k $\Omega$ 、帰還率 $\beta$  は $\frac{R_1}{R_1+R_2}=0.5$ である。

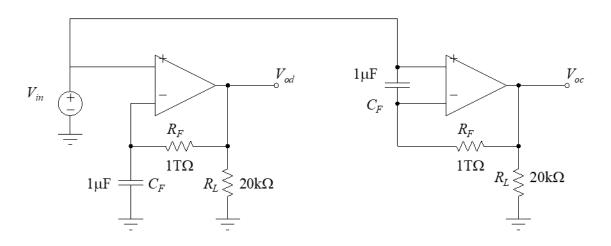

## 3.3.5 **直流利得** (DC Gain)

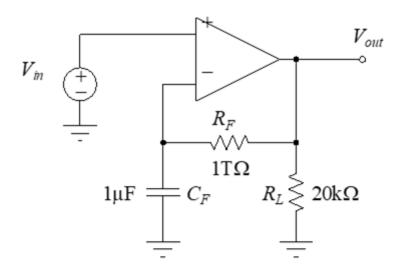

直流利得は図 3.10 に示す回路を用いて小信号解析を行い、直流利得を算出する。入力電圧には直流 0V、交流 1Vを用いる。

直流時、図 3.10 の回路は 1T  $\Omega$ の帰還抵抗によって負帰還構成となっているため、 回路の直流バイアスが定まる。また、入力信号の周波数が高くなるにつれて、反転入力 端子と接地点との間に接続される 1mF の容量のインピーダンスが小さくなるため、負 帰還量が 0 に近づき、反転入力端子が仮想的に接地している。このとき、回路が閉ルー プと同じ状態になり、出力には閉ループの利得倍された入力電圧が現れる。よって、出力端子での利得や位相特性は閉ループ時の特性とほぼ等しくなる。

シミュレーションによって得られた直流利得は出力特性の影響を受けたものであり、本来の直流利得ではない。そこで、次に示す補正計算を行い、本来の値を求める。実際の直流利得を $A_0$ とシミュレーションで算出値 $A_{0-sim}$ の関係を次式に示す。

$$A_0 = \frac{R_L + r_0}{R_L} A_{0-sim} \tag{3.2}$$

ここで、 $R_L=20k\Omega$ 、 $r_0$ は前項で算出した実際の出力抵抗である。

図 3.10 DC Gain, PM, GBP のシミュレーションに使用する回路

### 3.3.6 位相余裕(PM)

位相余裕は図 3.10 の回路を用いて小信号解析を行い、位相余裕を算出する。入力電 圧には直流 0V、交流 1Vを用いる。

一般的に、位相余裕は「閉ループ利得が 0dB になったとき、周波数において出力電圧の位相回転が 180 度になるのに必要な位相」と定義されている。従って、閉ループ利得が 0dB になった周波数における出力電圧の位相を求め、180°からその値を引いた値が位相余裕となる。しかし、前提としてこの定義は主要極以外の極及び零点の影響が十分無視できる。意図的に零点を挿入して局地的に位相回転を戻すと、一見して位相余裕のある演算増幅器に見えるが、ステップ応答の収束性が悪いなどの問題が発生する。そのため、評価には「180°から単一の利得帯域内の最大位相回転を引いた値の絶対値」を用いる。

#### 3.3.7 利得帯域幅積 (GBP)

利得帯域幅積は図 3.9 の回路を用いて小信号解析を行い、利得帯域幅積を算出する。 入力電圧には直収 0V、交流 1Vを用いる。

演算増幅器は開ループ利得が 0dB 以上の周波数特性において、単一の極しか持たないように設計されるのが一般的である。この極を主要極と呼ぶ。このため、演算族服着の開ループ利得をボード線図上にプロットした際、主要極より高い周波数帯域で利得が-20dB/decの傾きで減衰する。このとき、任意の周波数とその周波数における演算増幅器の開ループ利得の積は一定となり、それを「利得帯域幅積」と呼ぶ。

主要極以外の極または零点が十分高い周波数にあり、その影響を無視できる場合、演算増幅器の開ループ利得が 0dB になった際も同じ傾きを持つ。よってこの場合、開ループ利得が 0dB になったときの周波数は利得帯域幅積と等しくなる。直流から開ループ特性が 0dB になった周波数までの帯域を単一利得帯域と呼ぶ。

評価には、以下の2項目のうち小さい方の値を用いる。

- ・開ループ利得が 0dB になったときの周波数

- ・開ループ利得が直流利得の平方根になった周波数と利得の積

#### 3.3.8 入力換算雑音 (IRN)

入力換算雑音は図 3.8 の回路を用いて小信号解析及び雑音解析を行い、入力換算雑音を求める。評価する値は、0.1Hz から 1MHz までの入力換算雑音の積分値である。ただし、図 3.8 中の帰還抵抗には熱雑音を生じない抵抗モデルを用いる。帰還抵抗にこのモデルを適用することで、演算増幅器のみの熱雑音を評価できる。

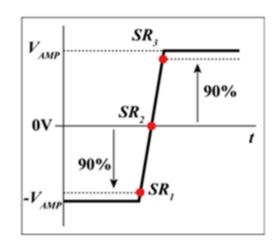

#### 3.3.9 スルーレート (SR)

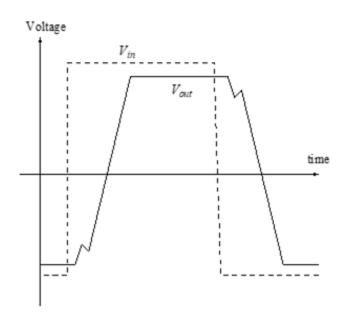

図 3.8 のテストベンチを用いて過渡解析を行い、スルーレートを求める。入力電圧は立ち上がり及び立下り共に傾きが 100V/ns となるようなステップ電圧を印加する。例として $\pm 1.5V$  の電圧振幅変化の場合、遷移時間は 0.03ns となる。スルーレートの評価方法について図 3.9 を例にして説明する。ここで、 $V_{AMP}$ 及び $-V_{AMP}$ は、それぞれ立ち上がる前の出力電圧の値と収束した後の出力電圧の値である。スルーレートの値は次式から求める。

$$SR = \frac{SR_1 + SR_2 + SR_3}{3} \tag{3.3}$$

ここで、 $SR_1$ 、 $SR_2$ 、 $SR_3$ はそれぞれ $V_{OUT}$ が-90%のときの傾き、0V のときの傾き、+90% のときの傾きである。図 3.11 は立ち上がりの場合の例である。立ち上がりも同様の計算を行い、小さい方の値をスルーレートとして評価する。

図 3.11 SR (立ち上がり) の例

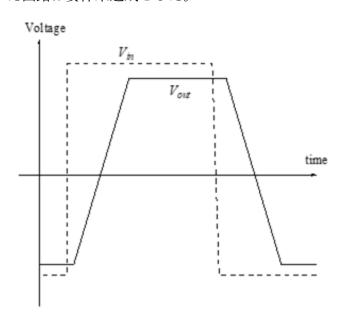

スルーレートの評価では、「スルーレートの評価で検出される出力電圧波形の立ち上がり及び立下りが1つしか存在しない」という要件を満たすため、波形の立ち上がり及び立ち下り回数を確認する。要件を満たす出力電圧波形の例を図3.12、要件を満たさない出力電圧波形を図3.13に示す。図3.13のように複数の立ち上がりが存在する出力電圧波形が確認された回路は要件未達成とした。

図 3.12 要件を満たした出力波形の例

図 3.13 要件を満たしていない出力波形の例

#### 3.3.10 全高調波歪 (THD)

全高調波歪は図 3.8 に示す回路を用いてフーリエ解析と過渡解析を行い、算出する。電源電圧はそれぞれ 0V から  $V_{DD}$ 及び 0V から  $V_{SS}$ へと変化するステップ入力を加える。入力電圧は周波数 100 Hz、振幅 2.5 mV の正弦波とし、電源電圧のステップが変化してから 1 ms 後に加える。全高調波歪は回路の出力が定常状態となる部分で評価する。評価するためには基本波の 1 波分のデータがあれば十分であるため、評価には 最後の 1 波(10 ms)の結果のみ用いる。ここで、重要となる部分が 1 波分のデータポイント数である。データポイントを多く取得する程、計算精度は向上するが、一般的に、基本波の周期の 1/100 の間隔でデータを出力する。つまり、1 波当たり 100 ポイントのデータがあれば高精度で求めることが可能である。そのため、本研究では 1 波当たり 100 点のデータポイントを取り、このときの全高調波歪を評価に用いる。

#### 3.3.11 同相除去比(CMRR)

同相除去比は求めるために、図 3.13 の回路を用いて小信号解析を行う。入力電圧には直流 0V、交流 1V を用いる。このテストベンチは、開ループ利得を求めるための回路に、同相利得を求めるための回路を追加した構成である。同相利得を求めるための回路は、演算増幅器の入力端子の間に大きな容量を接続し、反転入力端子と出力端子の間に大きな帰還抵抗を接続する。直流では容量が開放となるため  $1T\Omega$  によって演算増幅器に負帰還がかかり、バイアス状態が決定される。入力周波数が高くなるにつれて容量のインピーダンスが小さくなり演算増幅器の入力端子が短絡される状態になる。また、帰還抵抗が大きな抵抗値を持つため、周波数が高くなると入力端子と出力端子が開放される状態になり、入力端子の電位が同じように変動する際の出力電圧が見られる。この出力電圧と入力電圧の比を同相利得  $A_c$ と呼び、次式で定義する。

$$A_c = \frac{V_{oc}}{V_{in}} \tag{3.4}$$

一方、演算増幅器の開ループ利得は差動利得 A<sub>d</sub>と呼び、次式で与えられる。

$$A_d = \frac{V_{od}}{V_{in}} \tag{3.5}$$

CMRR は差動利得  $A_d$ を同相利得  $A_c$ で割ったものであり、次式より求められる。

$$CMRR = \frac{A_d}{A_c} = \frac{V_{od}}{V_{in}} \tag{3.6}$$

評価には、周波数 0.1Hz における CMRR を使用する。

図 3.14 CMRR のシミュレーションに使用する回路

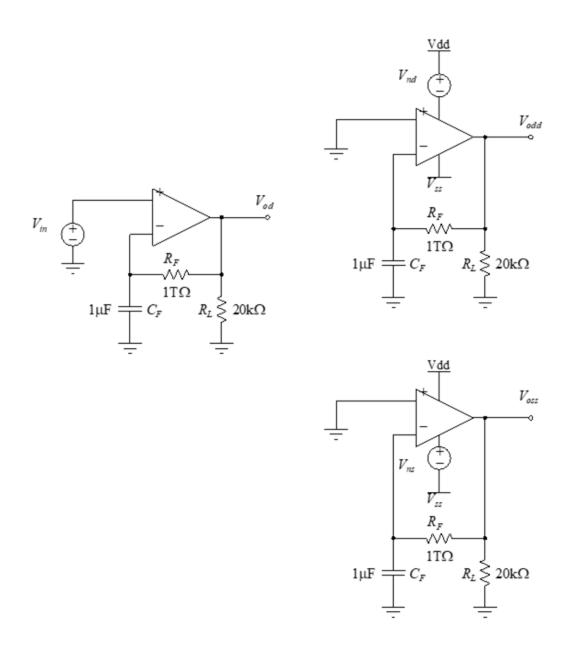

## 3.3.12 電源電圧変動除去比 (PSRR)

電源電圧変動除去比を求めるために、図 3.14 のテストベンチを用いて小信号解析を行う。入力電圧には直流 0V、交流 1V を用いる。電源と演算増幅器の電源端子の間に小信号電圧源を挿入し、入力端子 を接地した上で、出力電圧を求める。この際、 $V_{DD}$  と $V_{SS}$  の両方に同時に小信号源を挿入しない。演算増幅器の開ループ利得を  $A_{dd}$   $V_{SS}$  から出力への利得を  $A_{ds}$   $V_{SS}$  から出力への利得を  $A_{ss}$  とすると、各々の PSRR は以下の式で算出でき、周波数 0.1Hz における両者のうち、小さい方の値を PSRR とする。

$$PSRR_{V_{dd}} = \frac{A_d}{A_{dd}} \tag{3.7}$$

$$PSRR_{V_{SS}} = \frac{A_S}{A_{SS}} \tag{3.8}$$

図 3.15 PSRR のシミュレーションに使用する回路

#### 3.3.13 同相入力範囲(CMIR)

同相入力範囲は図 3.15 の回路を用いて直流解析を行い、同相入力範囲を算出する。 出力電圧の誤差が5%以下である入力電圧範囲を評価に用いる。演算増幅器は多くの場 合、負帰還を掛けて使用する。この際、入力端子間は仮想短絡となり同電位となる。特 に、非反転入力端子が接地されている場合反転入力端子の電位も接地電位と等しくなり、 仮想接地となる。一方、正相増幅器を構成する場合、演算増幅器の両入力端子は入力電 圧に追従するため、入力可能な電圧は演算増幅器の同相入力電圧範囲で決まる。同相入 力電圧範囲を求めるには、演算増幅器の両入力端子が接地されていない構成を用いる。 しかし、正相増幅回路用いると広い入力範囲を有する演算増幅器の場合、同相入力電圧 範囲が検出される前に出力電圧が飽和し、正しく評価できない。正しく評価するために は、回路の利得をなるべく小さくする必要があるが、小さすぎると出力電圧の誤差が大 きくなり、検出条件の誤差 5%以内を満たすことが困難である。そこで、評価する演算 増幅器の後段に利得 10 倍の理想増幅回路(電圧制御電圧源)を接続し、出力電圧を増幅 させる。テストベンチでは利得が-0.5 倍となっており、入力電圧は電源電圧の 2 倍で変 化するため、出力電圧は電源電圧まで変化する。一方、評価する演算増幅回路の出力電 圧は、10 倍の増幅器により電源電圧の 1/10 しか変化しない。これは出力電圧の要件に 等しい値であり、出力段の特性が評価に影響しないための工夫である。演算増幅器の入 力端子の同相電圧は入力電圧の半分なので、この場合は電源電圧まで変動する。同相入 力範囲は出力電圧の誤差(理論値と解析値との差)で評価するが、演算増幅器がオフセッ トを持つ場合、そのオフセットが出力に現れ、誤差として検出される。その影響を排除 するために、解析から得られた出力電圧からオフセット電圧を引いたものを用いて、次 式を満たす入力電圧を求める。

$$1 - \frac{|V_{out} - V_{os}|}{GV_{in}} < 0.05 \tag{3.9}$$

この時に得られた最大と最小入力電圧を  $V_{inmax}$  と  $V_{inmin}$  とした場合、同相入力電圧範囲  $V_{cmr}$  は次式で求められる。

$$V_{cmr} = 0.5(V_{inmax} - V_{inmin}) (3.10)$$

最後に、同相入力範囲の評価に用いる値 CMIR は次式で求められる。

$$CMIR = \frac{V_{cmr}}{V_{DD} - V_{SS}} \times 100\% \tag{3.11}$$

図 3.16 CMIR のシミュレーションに使用する回路

## 3.3.14 出力電圧範囲 (OVR)

出力電圧範囲は図 3.17 の回路を用いて直流解析を行い、算出する。評価には出力電圧の誤差が 5%以下である出力電圧範囲を用いる。出力電圧範囲は演算増幅器の入力

端子が接地電位に固定されている構成を用いて評価する。評価回路は利得が-1 倍の反転増幅器を用いる。演算増幅器がオフセットを持つと、それが出力電圧の誤差として現れる。この項目で評価する出力電圧はオフセット分を除いたものであるため、次式で出力電圧範囲  $V_{or}$ を求める。

$$1 - \frac{|V_{out} - V_{OS})|}{V_{in}} < 0.05 \tag{3.12}$$

最後に出力電圧範囲の評価に用いる OVR は次式で求める。

$$OVR = \frac{V_{or}}{V_{DD} - V_{SS}} \times 100\%$$

(3.13)

図 3.17 OVR のシミュレーションに使用する回路

## 3.3.15 最低要件

本研究における回路特性の最低要件を表 3.4 にまとめる。

表 3.4 回路特性の最低要件

| 評価項目            | 設計最低要件              |  |

|-----------------|---------------------|--|

| 電源電圧(SV)        | Rail-to-rail電圧が3V以下 |  |

| 消費電流(CC)        | (変動に関する条件)          |  |

| 消費電力(PD)        | 100mW以下             |  |

| 出力抵抗(OR)        | 無し                  |  |

| 直流利得(DCgain)    | 40dB以上              |  |

| 位相余裕(PM)        | 45deg以上             |  |

| 利得帯域幅積(GBP)     | 1MHz以上              |  |

| 入力換算雑音(IRN)     | 無し                  |  |

| スルーレート (SR)     | 0.1eV/us以上          |  |

| 全高調波歪(THD)      | 1.0%以下              |  |

| 同相除去比(CMRR)     | 40dB以上              |  |

| 電源電圧変動除去比(PSRR) | 40dB以上              |  |

| 出力電圧範囲(OVR)     | 5.0%以上              |  |

| 同相入力範囲(CMIR)    | 5.0%以上              |  |

# 第4章 遺伝的アルゴリズムと動的計画法 を複合した素子値の自動設計

## 4.1 遺伝的アルゴリズム (GA) と動的計画法 (DP)

#### 4.1.1 GA と DP の特徴

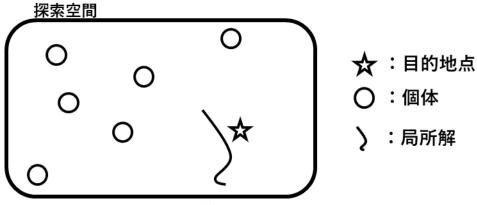

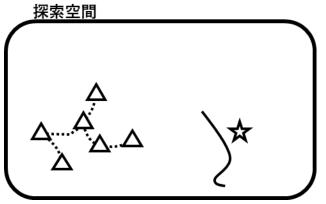

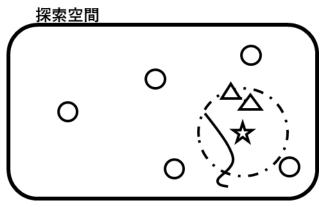

GAは一定数の初期集団が持つ遺伝子とその掛け合わせが探索範囲となるため巨視的にみれば範囲と多様性は豊富だが、微視的にみると探索されるのは離散的な部分だけである。従って、広大な探索範囲から解の周辺にたどり着くのは比較的容易だが、そこから真の解まで到達するのは難しい。そのため、GAでは一定条件で新たな初期値を投入したり、突然変異によって初期値とは異なる個体を生み出し、初期値依存や局所解へ陥ることへの対策としている。また、GAが学習していく挙動を表すならば、探索空間の中に無作為に点在する個体が世代を経ることで、徐々に解方向へ存在を移しながら近づいていく。

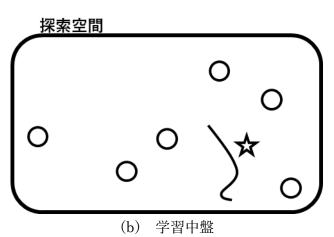

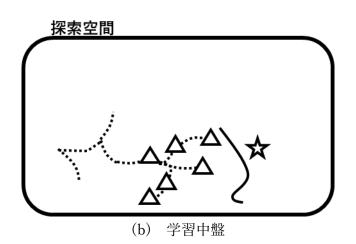

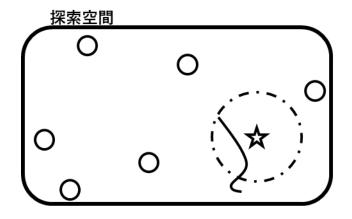

一方、DP は巨視的に見れば探索範囲は狭いものの、微視的に見れば探索経路は一定間隔の単調列で表せ、連続的な変化を可能とする。しかし、初期値から連続的に到達できる場所でなければ解を導けない。DP では異なる初期値から学習をリスタートすることで初期値依存や局所解への対策としている。DP による学習は、初期地点から枝分かれするように道順を作りながら、解がある方向へ進んでいく。それぞれの学習している様子を二次元化したイメージを図4.1と図4.2に示す。

(a) 学習序盤

図4.1 GA が学習する挙動のイメージ

(a) 学習序盤

☆ :目的地点

▲ :エージェント

〉 :局所解

...: : 移動経路

図4.2 DP による学習のイメージ

### 4.1.2 素子値の自動設計への応用

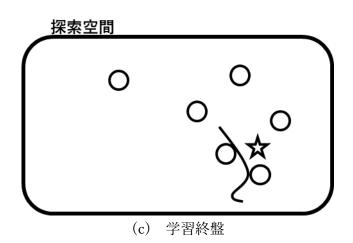

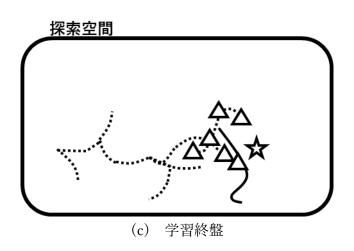

本章では GA と DP を組み合わせて素子値の自動設計を行う。GA では解の近傍から真の解へ辿り着くことは困難であるが、DP によって細かくエージェントを動かすことで解へ辿り着きやすくなる。また、DP は結果が初期値に依存するところが大きいが、GA によって解の近傍までたどり着けることや、異なる初期値を持つ複数のエージェントによって学習を行えることから、解へと辿り付きやすくなる。探索の手順としては、探索の序盤は GA の挙動を行い、広い探索空間から解を探索し始める。世代を重ねるごとに個体集団は近づいていき、設計者が定める閾値を評価値が超えた個体をエージェントとして行動させる。エージェントは DP による学習で GA よりも探索空間を細かく移動する。GA の個体集団から評価値が閾値を超えた個体が現れるごとに、その個体をエージェントとする。これにより、終盤では異なる初期値を持ったエージェントが複数存在し、探索できる。GA と DP を複合した探索の挙動を二次元化したイメージを図 4.3 に示す。

:目的地点 :個体

:エージェント

:局所解

:移動経路

(,):閾値

(a) 学習序盤

(b) 学習中盤

(c) 学習終盤

図 4.3 GAと DP を複合した学習のイメージ

## 4.2 素子値の自動決定手順

### 4.2.1 初期値の作成

初期集団の作成方法について説明する。設計者はプログラムに任意のネットリストを与える。ネットリストは第3章と同様に SPICE 形式に従う。プログラムは与えられたネットリストから素子を判定する。抵抗であれば抵抗値、MSOFET でチャネル幅のパラメータを探索するために、表 4.1 に示す範囲でランダムに値を与える。本章では探索範囲を制限するために MOSFET のチャネル長は  $1.0\,\mu$  m で固定した。

パラメータ 最大値 最小値 間隔 抵抗 9900kΩ 100kΩ 100kΩ チャネル幅 50.0μm 0.2μm 0.1μm

表 4.1 パラメータの取りうる範囲

## 4.2.2 環境適応度

第3章と同様に、個体の優劣を環境適応度(適応度)は二段階の評価によって算出する。一段階目は各特性が最低要項を満たした割合で算出し、各項目につき1が最大値となる。一段階目の評価方法は表3.1と同様である。全ての項目において最低要項を満たした場合のみ二段階目の評価方法によって各特性の評価値が適応度に加算される。二段階目は各特性が目標値とどれだけ近いかで算出される。二段階目の評価方法を表4.2に示す。

| 目標値を満足する条件 | 結果が目標値より大きい | 結果が目標値よりも小さい |

|------------|-------------|--------------|

| 目標値        | 目標値結果       |              |

| 口惊胆        | 結果          | 目標値          |

| 項目外        | 0           | 0            |

表 4.2 評価方法

### 4.2.3 個体からエージェントへの進化

個体の評価が終わった時点で、4.2.2 で示す適応度が任意の閾値を超えた個体はエージェントなる。個体は個体集団全体でスキーマを学習させるための要素であり、個体自体に学習機能はない。一方で、エージェントはそれ自体が行動価値を持ち、学習機能を持っているため、本稿では個体からエージェントへの移行を「進化」と呼ぶ。個体から進化したエージェントは進化した時点でのパラメータを初期値として、自身の持つパラメータ(状態)を少しずつ変化させながら、独自に行動価値を学習しながら探索を進める。ここで独自に探索するエージェントに一定の探索回数を設けると、エージェントの増加とともに、シミュレーション時間が膨大になってしまう。しかし、同一の初期値を持つエージェントが一つしかないと十分な探索が行えない可能性が高い。そこで、閾値を超えた個体と近似な個体もまとめて、同一の初期値を与えてエージェントへ進化させる。これは探索回数の確保と、多様性の減少を防ぐ目的がある。また、エージェントの行動は1世代の中で、エージェント1つにつき、新たな状態に遷移するか、指定回数に至るまで行う。

## 4.3.4 GA による遺伝子操作

#### (a) 選択(淘汰)

「選択」は第3章と同様にエリート個体保存戦略と、トーナメント選択を用いる。このとき、エージェントは選択対象から外す。エリート個体保存戦略は常に評価の高い個体が残るため、個体集団内でエリートの持つスキーマが増殖し支配的になりやすい。言い換えれば多様性が減少していく。しかし、学習が進むにつれて複数のエージェントが現れ、それらは異なる初期値を持っていることが望ましい。従って、個体集団内の多様性の減少を防ぎたい。エージェントは閾値を超えた個体とその近似個体が進化したものであるため、似通ったスキーマを持っている。選択の際にエージェントを対象から除くことで、エージェントが持つスキーマが個体集団内で増殖するのを防ぐ。

#### (b) 交叉

「交叉」でも第3章と同様に多点交叉を用い、2つの個体でランダムに選んだ複数の素子で抵抗値もしくはチャネル長、チャネル幅のいずれかを交換する。エージェントが除かれた状態で世代交代を繰り返すと、個体集団ではエージェントが持ちえないスキー

マが支配的になっていると考えられる。そのため、低確率で個体を個体集団の中からではなく、エージェントの一つから選び、交叉を行う。

#### (c) 突然変異

「突然変異」では個体が持つ素子値のうち一つを変化させる。変化可能な値の範囲は表 4.1 に示されているものを同じである。「突然変異」にはいくつかの種類があるが、本項ではエージェントによって、細かい探索が行われる。そのためここでは、素子値を完全にランダムで選びなおす。

### 4.3.5 DP による探索

#### (a) 行動価値

エージェントの行動によって環境が状態 s から状態  $s_{t+1}$  に遷移すると、それに応じた報酬  $r_t$  がエージェントに与えられる。言い換えれば、この報酬は即時的なものであり、次の行動の評価を表すものでしかない。しかし、一時的に評価が高くでも、それが最終的に目的に到達する過程に十分な行動とは限らない。強化学習の説明で頻繁に例に上がる囲碁や将棋に例えると、一時的に有利になる手を選んでばかりいても、数手先の動きを予測できる熟練者には簡単に対処されてしまい勝利できない。従って、エージェントが状態 s から状態  $s_{t+1}$  に遷移するための行動の良悪は、報酬を用いた長期的な価値によって表現されるべきである。

長期的な価値を表現するものとして Q-Leaning において Q 値を更新する式を用いる。 Q値とは"状態行動価値"とも呼ばれ、「ある状態 s において、ある行動 a をとった場合の価値」を示すものである。 Q 値は学習を重ねるごとに更新されていき、1 つ先の遷移先である時点 t+1 での Q 値を考慮し、次式で表される。

$$Q(s_t, a_t) \leftarrow (1 - \alpha)Q(s_t, a_t) + \alpha[r_{t+1} + \gamma \max Q(s_{t+1}, a_{t+1})]$$

4.1

$\alpha$  は学習率と呼ばれ、Q 値の更新の大きさを制御する値である。 $Q(s_t,a_t)$  は時点 t での状態  $s_t$  からみた行動  $a_t$  に対する Q 値である。 $r_{t+1}$  は報酬であり、状態  $s_t$  から状態  $s_{t+1}$  への行動に対する評価になる。また、 $maxQ(s_{t+1},a_{t+1})$  は 1 つ先の遷移先である時点 t+1 における状態  $s_{t+1}$  から見える Q 値の最大値であり、先の状態への期待値を示す。学習ではこの値を  $\gamma$  によって制御する。

#### (b) 学習テーブル

学習テーブルは状態と行動をまとめたもので、各状態で行動に対応する行動価値を持っている。しかし、状態を「回路が持つ素子値」にしているため、全ての状態と行動に対してテーブルを保持しておくのは無駄が多い。従って本研究では遺伝子操作や行動によって露わになった状態と行動のみを保持しておく。学習中、ある時点で到達していない状態から見える行動価値は0となる。

また、時点 t で状態  $s_t$  から状態  $s_{t+1}$  に行動 a によって遷移したときに行動価値の更新が行われるが、このとき、状態  $s_{t+1}$  から状態  $s_t$  に遷移するための行動は、行動-a である。つまり、時点 t+1 で行動-a によって状態  $s_{t+1}$  から状態  $s_t$  に遷移したときの行動価値も与えることができる。本研究ではこれにより学習の効率化を図る。

#### (c) 行動

エージェントが時点 t における状態  $s_t$  から時点 t+1 における状態  $s_{t+1}$  へ遷移するための動作を"行動"と呼ぶ。本章では素子値のサイジングを行うため、「どの素子をどれくらい変化させるか」を行動とした。しかし、素子によって素子地がとれる範囲は異なり、変化させるべきスケールも異なる。そこで、プログラムでは設定された倍率  $(-3\sim-1,+1\sim+3)$  だけを変化させることとした。つまり、素子値はその倍率のいずれかの値と、素子ごとに定められた定数値との積だけ、その素子値を変化させる。

行動選択は Epsilon-Greedy 法を用いる。行動選択を行動価値が大きい行動が優先されるようにすると、偶然に行動価値が大きくなった行動だけが常に選択されてしまう。そこで、確率 Epsilon 以下であればランダムで行動を選択させるようにする。これにより、様々な行動を行いながら次第に行動価値の学習が可能となる。

# 第5章 実行結果

## 5.1 ゲート端子の接続先探索の結果

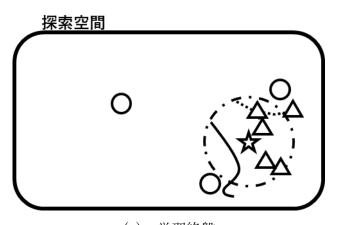

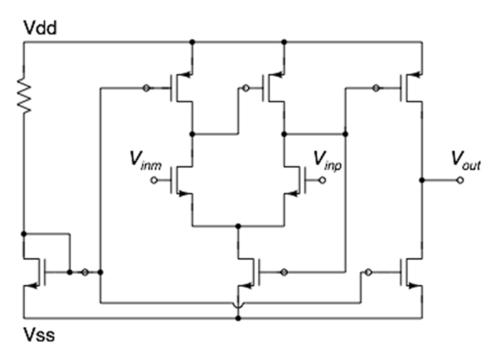

ゲート端子の接続先探索によって得られた結果を示す。ゲート端子の接続先を適切に探索できるかを検討するため、バイアス以外のゲート端子が接続されていない簡素な回路構成を用意した。その回路構成を図 5.1 に示す。また、ゲート端子の接続先を探索する際の GA のパラメータを表 5.1 に示す。

図 5.1 探索する回路の構成

表 5.1 GA のパラメータ

| 世代数     | 10世代  |  |

|---------|-------|--|

| 個体数     | 50個体  |  |

| トーナメント数 | 4個体ずつ |  |

| 交叉率     | 80%   |  |

| 突然変異率   | 5%    |  |

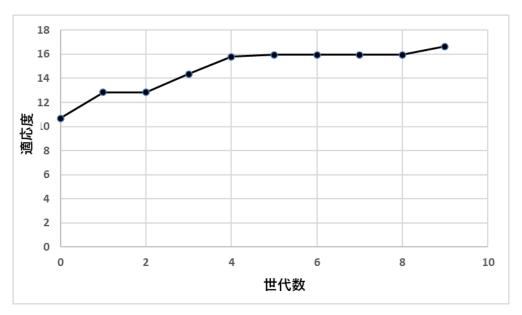

探索によって出力された回路の、目標仕様と回路特性を表 5.2 に示す。また、学習経過となる世代数と適応度のグラフを図 5.2 に、最終的に出力された回路の構成を図 5.3 に示す。図 5.2 よりランダムによって生成された初期個体は目標値を満たさず、その後数世代に渡って回路構成が変化しても目標を満たすことはできない。しかし、世代を重ねるたびに学習によって回路特性が向上し、目標仕様満たすことが確認された。

表 5.2 回路特性の目標値と結果

| 特性                    | 最低要件      | 目標値      | 結果       |

|-----------------------|-----------|----------|----------|

| CC [A]                | 無し        | 無し       | 4.36E-04 |

| PD[W]                 | 100mW以下   | 4.00E-05 | 1.31E-03 |

| DC Gain [dB]          | 40dB以上    | 6.00E+01 | 5.58E+01 |

| PM [°]                | 45°以上     | 6.00E+01 | 1.71E+02 |

| GBW [Hz]              | 1MHz以上    | 1.40E+07 | 4.07E+08 |

| SR [V/s]              | 0.1V/us以上 | 1.00E+07 | 9.91E+09 |

| THD [%]               | 1%以下      | 5.00E-01 | 4.82E-01 |

| CMRR [dB]             | 40dB以上    | 5.00E+01 | 1.41E+03 |

| PSRR [dB]             | 40dB以上    | 5.00E+01 | 6.41E+01 |

| OVR [%]               | 5%以上      | 5.00E+01 | 2.90E+01 |

| CMR [%]               | 5%以上      | 5.00E+01 | 7.71E+01 |

| CA [um <sup>2</sup> ] | 1mm^2以下   | 1.00E+09 | 2.29E+04 |

図 5.2 世代数と適応度の関係

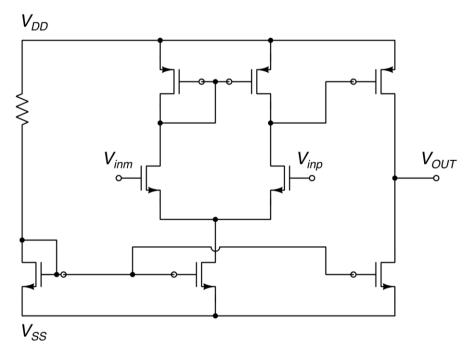

図 5.3 出力された回路構成

## 5.2 GA と DP を複合した素子値設計の結果

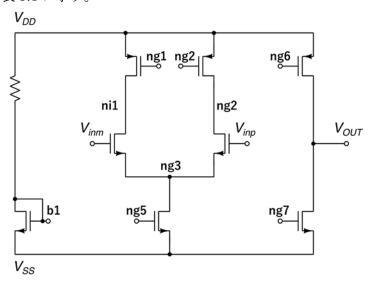

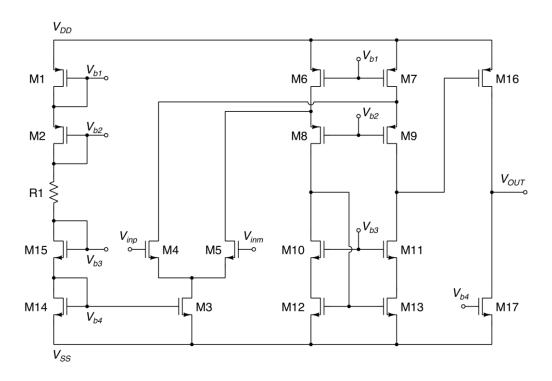

GA と DP を複合して素子値を決定した場合、GA で素子値を決定するのと比較して どの程度回路特性が向上したかを示す。使用した回路構成を図 5.4 に示す。また、学習 は表 5.3 に示すパラメータで GA 及び DP の学習を行った。

図 5.4 自動設計する回路

表 5.3 学習のパラメータ

| GA | 世代数     | 150世代 |  |

|----|---------|-------|--|

|    | 個体数     | 100個体 |  |

|    | トーナメント数 | 3個体ずつ |  |

|    | 交叉率     | 80%   |  |

|    | 突然変異率   | 5%    |  |

|    | 変動率     | 10%   |  |

| DP | 3       | 0.3   |  |

|    | 学習率     | 0.1   |  |

|    | 割引率     | 0.9   |  |

|    | 行動の最大数  | 200回  |  |

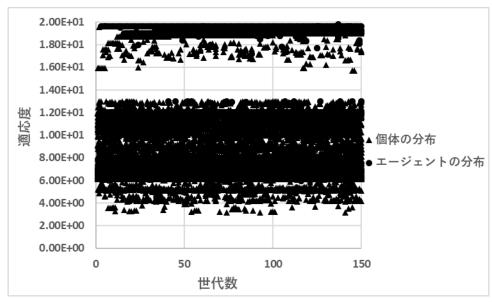

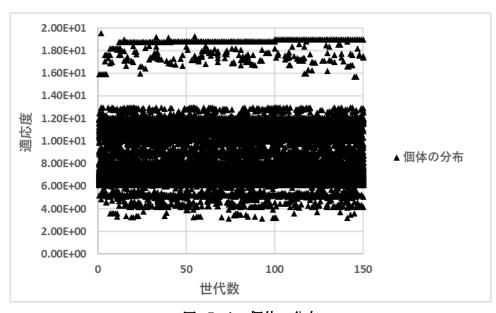

学習した結果として、図 5.5 に世代数と適応度(評価値)の分布図を示す。図 5.5 において GA 部分の探索により設計された回路の適応度の最大値は 19.60 で、DP 部分による学習により設計された回路の評価値の最大値は 19.77 である。従って、個体から進化したエージェントの学習によって、回路特性が向上した。また、最終的に出力された結果と GA のみで学習を行った結果を表 5.4 に示す。表 5.4 から、GA 単体で探索を行うよりも、探索範囲の異なるアルゴリズムである DP を複合させることによって設計精度が向上することが確認できた。

図 5.5 エージェントと個体の分布

図 5.6 個体の分布

図 5.7 エージェントの分布

| 特性           | 目標値      | GAによる結果  | 結果       |

|--------------|----------|----------|----------|

| CC [A]       | 2.00E-05 | 1.62E-05 | 2.34E-05 |

| PD [W]       | 6.00E-05 | 4.88E-05 | 7.02E-05 |

| DC Gain [dB] | 7.00E+01 | 6.15E+01 | 5.00E+01 |

| PM [°]       | 5.00E+01 | 4.69E+01 | 4.95E+01 |

| GBW [Hz]     | 1.00E+07 | 1.19E+07 | 6.05E+06 |

| SR [V/s]     | 2.00E+08 | 3.67E+06 | 2.35E+07 |

| THD [%]      |          | 4.82E-01 | 4.52E-01 |

| CMRR [dB]    |          | 8.70E+02 | 2.38E+02 |

| PSRR [dB]    |          | 5.88E+01 | 4.79E+01 |

| OVR [%]      |          | 4.87E+01 | 4.89E+01 |

| CMR [%]      | 7.00E+01 | 4.28E+01 | 6.47E+01 |

| OR [Ω]       | 5.00E+03 | 6.45E+03 | 2.49E+03 |

| IRN [Hz]     | 3.00E-02 | 5.60E-02 | 4.17E-02 |

| Fitness      | 22.0     | 19.2     | 19.8     |

表 5.4 回路特性の目標値と結果

# 第6章 まとめと今後の課題

## 6.1 まとめ

本論文では回路の自動合成のために、ゲート端子の接続先の自動決定と、GAとDPを組み合わせて素子値決定を行うことで、自動合成精度を向上させる手法について提案した。ゲート端子の接続先はランダムに選択しても目標値を満足する確率は低く、アルゴリズムを用いて探索を行うことで、同じ電流経路を持つ回路構成であっても目標値を満足する回路構成足りえることが確認できた。また、GAとDPを組み合わせて素子値決定を行うことで、互いのアルゴリズムの短所を補い、単一のアルゴリズムよりも精度を向上させることができた。

## 6.2 今後の課題

自動合成のシステムに本論文で提案したゲート端子の接続先探索を実装することが第一の課題である。しかし、自動合成にゲート探索のステップを含めることで、シミュレーション回数が増えることは明白である。従って、ゲート端子探索の探索時間を短縮することが望まれる。現在の方法は GA というメジャーな手法を使用したが、より高度なアルゴリズムを用いることで冗長性を減らし短期間で探索を実現することが重要である。

また、素子値設計では、学習序盤でGAが達成できる閾値や目標値でなければ、DPによる学習にたどり着けないため、閾値の設定が難しい。特に、自動合成中に生成される回路の特性や傾向は多岐にわたるため、システム内で自動的に閾値を判別するステップや学習が望まれる。

# 謝辞

本研究を進めるにあたり、有益な助言を頂いた所属研究室の髙井伸和准教授、同期の 猿田将大氏、新井信吾氏、同研究分野の斎藤彰寛氏、長嶋宜彦氏、中島望夢氏、 加藤博己、酒向諒、蓮沼尚也に心より感謝申し上げます。また、論文審査をして頂きま した、伊藤直史准教授、弓仲康史准教授に心より感謝申し上げます。

# 参考文献

- [1] Hajime Sibata, Nobuo Fujii: "Automatic Synthesis of Transistor Circuit Focusing on Current Path", ECT-00-13, pp.71-76, Dec. 1999.

- [2] 鈴木 研人, 髙井 伸和, 菅原 誉士紀, 大河内 一登, 吉澤 慧, 石井 司, 篠田 沙樹, 福田 雅史, "数式ベースと遺伝的アルゴリズムの組み合わせによる演算増幅器の自動設計," 電子情報通信学会 集積回路研究会(ICD), EMD2016-83, pp.69-74, 広島, Jan. 2017.

- [3] Hajime Sibata, Nobuo Fujii: "Automatic Synthesis of Analog Circuits Using Uniform Cells", ECT-02-55, pp.23-28, Mar. 2002.

- [4] Satoshi Konno, Nobukazu Takai, "Automatic designof decipherable OP-Amp topology," 電気学会 電子・情報・システム部門大会, 沖縄, Sep. 2019

- [5] M.M. Hershenson, S.P. Boy, T.H. Lee, "Optimal Design of a CMOS Op-Amp via GeometricProgramming," IEEE Transactions on Computer-Aided Design, Volume 22, No.1, pp.1-21, Jan. 2001.

- [6] 竹原 裕司 , 夏井 雅典 , 田所 嘉昭, "GA を用いたオペアンプの最適素子値探索における個体表現の検討," 電気学会電子回路研究会, ECT-08-27, pp.41-46, Mar 2008.

- [7] JIANHAI YU, ZHIGANG MAO, "A Design Method in CMOS Operational Amplifier Optimization Based on Adaptive Genetic Algorithm," WSEAS Transactions on Circuits and Systems archive, Volume 8 Issue 7, Pages 548-558, July 2009

- [8] 猿田 将大, 高井 伸和, 今野 哲史, "高速·低消費電力のコンパレータを実現する Q-Leaning による素子値の自己改良,"電気学会 電子回路研究会, 山口, Jun. 2019.

- [9] 福田 雅史, 髙井 伸和, 猿田 将大," Q-learning を用いた自己改良モデルによる演算 増幅器の素子決定," 電気学会 電子回路研究会, 横河電機株式会社本社会議室, Mar. 2019.

- [10] 松場 輝樹 髙井 伸和,福田 雅史,久保 友助,"深層学習を用いた最適アナログ回路トポロジーの推論,"電気学会 電子回路研究会,ECT-18-076, 筑波大学,Oct. 2018.

- [11] Ziga Rojec, Jernej Olensek, Lztok Fajfar, "Analog Circuit Topology Representation for Automated Synthesis and Optimaization," Journal of Microelectronics, Electronic Components and Materials. Vol48, No.1(2018), 29-40.

- [12] 2020 年演算増幅器設計コンテスト, https://www.ec.ict.e.titech.ac.jp/opamp/2020/index.html

## 学会成果

- (1) 今野哲史, 高井 伸和, "遺伝的アルゴリズムを用いた演算増幅器のトポロジー及び素子パラメータ決定,"電気学会 電子回路研究会, ECT-19-031, 横河電機, Mar. 2019.

- (2) 今野哲史, 髙井 伸和, "遺伝的アルゴリズムによるノードが接続可能な点を仮定した演算増幅器の自動設計," 第9回 電気学会 東京支部 栃木・群馬支所 合同研究発表会, ETG-19-67, pp. 205-208, 小山工業高等専門学校, Mar. 2019.

- (3) Satoshi Konno, Nobukazu Takai, "Automatic designof decipherable OP-Amp topology," 電気学会 電子・情報・システム部門大会, pp.1554-1556, 沖縄, Sep. 2019.

- (4) 猿田 将大, 髙井 伸和, 今野 哲史, "高速・低消費電力のコンパレータを実現する Q-Leaningによる素子値の自己改良,"電気学会 電子回路研究会, ECT-19-035, 山口, Jun. 2019.

- (5) Akihiro Saito, Nobukaze Takai, Satoshi Konno, "Determination of circuit topology and element values from desired characteristics by machine learning," IEEE International Conference on Electronics on Electronics, Circuit and Systems (ICECS) Jul. 2020.